Система Delta Design обладает уникальным инструментарием для моделирования работы цифровой аппаратуры. Средства моделирования системы обеспечивают расчет и анализ совместной работы аппаратной части радиоэлектронного устройства и программного обеспечения (прошивки), которое функционирует на данном устройстве. Такой подход обеспечивает целостность данных моделирования, благодаря тому, что различные процессы совместно моделируются в одной среде, а не отдельно друг от друга.

Средства моделирования работы цифровой аппаратуры Delta Design предоставляют проектировщику следующие возможности:

Разрабатывать модели работы различных цифровых устройств |

Использовать готовые сторонние модели работы цифровых устройств, которые соответствую стандарту VHDL |

Разрабатывать программное обеспечение, которое способно функционировать, как на моделях устройств, так и на реальных системах |

Использовать стороннее программное обеспечение (прошивки), адаптируя его для разрабатываемого устройства |

Проводить моделирование работы как аппаратной части устройства, так и совместной работы аппаратной части и программного обеспечения (прошивки) |

Получать данные моделирования, в том числе визуальные, непосредственно в процессе расчета |

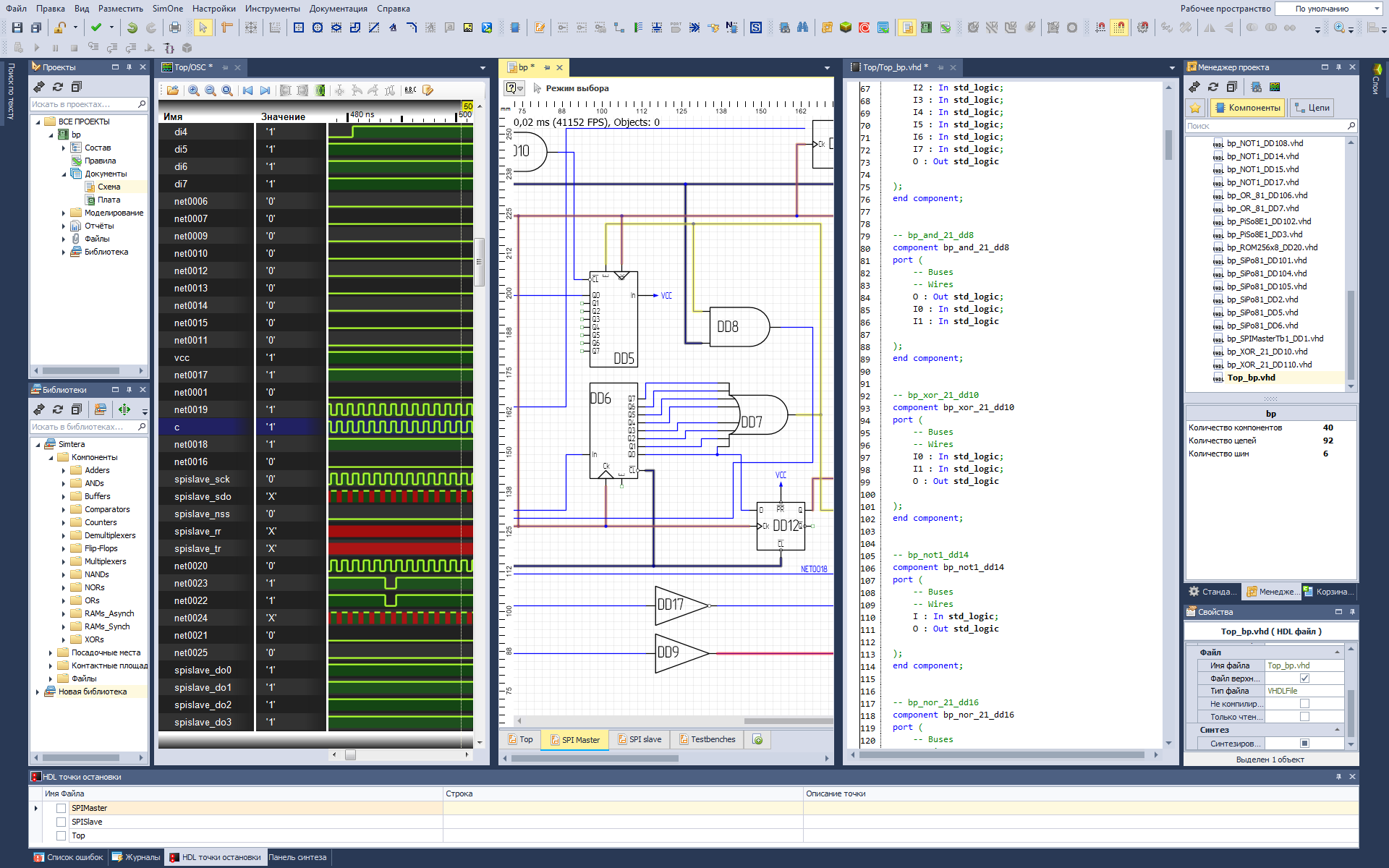

Цифровое моделирование в Delta Design производится благодаря модулю Delta Design Simtera, работающего на основе описания работы устройств на HDL-языках (Verilog/SystemVerilog/VHDL).

Для пользователей предусмотрены два режима работы – упрощенный и продвинутый.

Упрощенный тип работы обладает всей функциональной мощью продвинутого, но при этом ориентирован на схемотехников и специалистов, не знакомых с HDL-языками. В систему встроены инструменты работы с цифровым моделированием в схемотехническом виде, помогающим пользователю на любом из этапов флоу проектирования «библиотека»-«схема»-«моделирование». Пользователю необходимо лишь создать библиотеку компонентов с условно-графическим обозначением и привязать к компонентам HDL-модели. В системе предусмотрена автогенерация HDL-кода по УГО, что в значительной мере упрощает наполнение библиотек. На этапе проектирования схемы пользователю доступны все схемотехнические инструменты – работа с шинами, портами, листами и пр. Для перехода к моделированию необходимо лишь нажать несколько кнопок и выбрать данные для отображения.

Продвинутое моделирование в Delta Design Simtera ориентировано на разработчиков ПЛИС, на специалистов по верификации и тестировщиков. Для них в системе предусмотрены инструменты ведения проектов в текстовом виде, в систему можно импортировать уже существующие HDL-проекты. Инструменты assertion-based verification, отладка с помощью точек остановки, осциллографы и списки наблюдений помогут при проектировании и верификации. Текущие результаты моделирования сразу доступны для просмотра и анализа. Встроенный осциллограф может отображать данные непосредственно в процессе расчета, что позволяет существенно уменьшить время обнаружения ошибок. Также, в процессе расчета, доступен единый стек вызовов, объединяющий информацию по прошивкам и аппаратной части.

Цикл проектирования конфигурации ПЛИС может быть продолжен в системе модулем синтеза. Синтез в базис библиотечных компонентов программируемых логических интегральных схем доступен для следующих устройств:

Intel:

- Cyclone IV

- Cyclone IV E

- Cyclone V

- Cyclone 10

- MAX10

- Arria 10 GX

Xilinx:

- Spartan-7

- Artix-7

- Kintex-7

- Virtex-7

Также доступно проектирование и моделирование смешанных проектов. В системе обеспечивается наиболее полная поддержка стандарта VHDL, полная поддержка стандартов Verilog (IEEE Std 1364-2001, IEEE Std 1800-2005, Verilog-AMS 2.3.1) в данной версии недоступна, частично поддержан стандарт IEEE Std 1364-2001.